在先进集成电路技术持续向3纳米及以下节点演进的过程中,环栅晶体管(GAAFET)凭借出色的栅控能力与可扩展性,成为下一代芯片的核心器件结构;而横向扩散金属氧化物半导体(LDMOS)器件作为电源管理芯片等领域的关键功率器件,在高电场、高电压工况下同样面临严峻可靠性挑战。近日,华东师范大学集成电路学院吴幸教授、周龙达副教授团队围绕两类核心器件的应变调控与缺陷定位难题分别取得重要进展,相关成果均发表于第64届国际可靠性物理研讨会(IEEE International Reliability Physics Symposium,IRPS 2026),为下一代高性能、高可靠芯片设计提供关键理论与技术支撑。

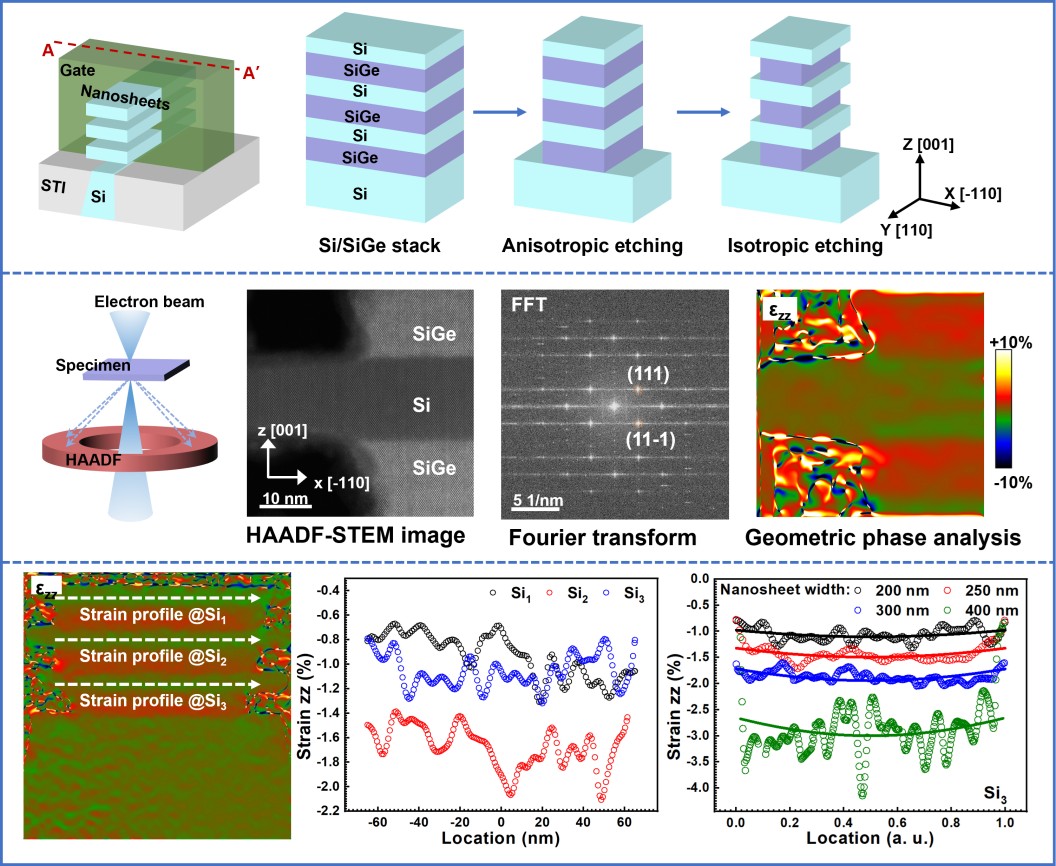

针对GAAFET器件微缩过程中传统应变工程带来的可靠性新问题,团队聚焦纳米片应变调控机制,利用先进原子尺度表征技术,首次实现纳米片宽度诱导应变变化的直接可视化观测。研究发现,GAAFET纳米片应变分布具有显著尺寸依赖特性:随着纳米片宽度增加,Si沟道压应变逐步增强,宽结构可有效抑制边缘应变松弛,该规律在底部纳米片层表现尤为突出,揭示出器件不同层间复杂的力学约束关系。通过多尺寸结构归一化分析,团队明确了应变从中心向边缘衰减的分布规律,从原子尺度建立起“结构尺寸—应变分布—器件性能”的内在关联,为先进器件应变工程优化与可靠性提升提供全新研究视角。相关成果以“Direct Visualization of Width-Induced Strain Variation in GAA Nanosheets at the Atomic Scale”为题发表于IRPS 2026,华东师范大学博士生李兰为第一作者。

图1:GAAFET纳米片的原子级应变分布。上方为GAAFET器件的示意图,中间为几何相位分析用于表征应变,下方展示了不同Si沟道、不同纳米片宽度的应变分布图。

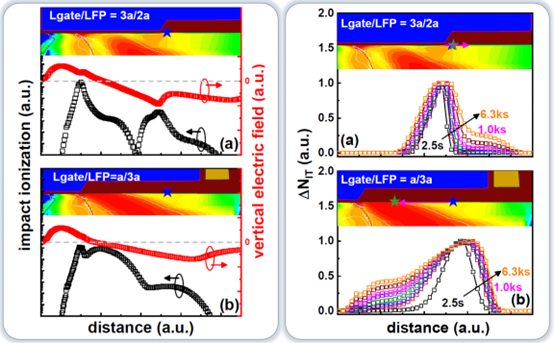

面向LDMOS器件热载流子退化(HCD)可靠性瓶颈,团队针对其缺陷空间分布广、关键退化位置难以精准识别的难题,创新提出一种简洁高效的缺陷定位斜率法。该方法基于器件关键电学参数特征斜率关系,无需复杂测试结构,在常规电学测量条件下即可实现关键缺陷区域的精准定位与动态追踪。结合实验与TCAD仿真,研究阐明缺陷位置由碰撞电离率与垂直电场分布共同决定,并清晰揭示器件几何结构对缺陷分布及演化路径的调控规律,为快速定位可靠性“热点”、优化LDMOS结构设计开辟了新路径,对提升电源管理芯片等关键应用的器件长期可靠性具有重要工程价值。研究通过直观的缺陷定位与演化分析,清晰刻画LDMOS器件早期退化阶段缺陷中心分布及随应力时间的演化路径,充分展现了新方法在揭示可靠性物理机制、追踪缺陷动态演化过程中的突出优势。相关成果以“A Slope Method for Critical-Region Defect-Center Localization in LDMOS under Hot-Carrier Degradation”为题发表于IRPS 2026,华东师范大学周龙达副教授为第一作者。

图2:提出的斜率法实现LDMOS关键缺陷的精准定位与动态追踪。左图为不同结构器件在早期退化阶段的缺陷中心位置提取结果,右图展示了缺陷中心随应力时间的演化路径,直观体现了该方法在揭示可靠性演化机制及缺陷演化过程方面的优势。

该工作也获得了该工作也获得了国家自然科学基金委、上海市科委探索者计划、重庆市自然科学基金以及华东师范大学原位先进器件研究中心的支持。