2025年6月8日至12日,超大规模集成电路研讨会(Symposium on VLSI Technology and Circuits,简称VLSI)在日本京都成功举办。原位中心2篇高水平学术论文入选。

一、基于FinFET先进工艺的低温CMOS可靠性研究

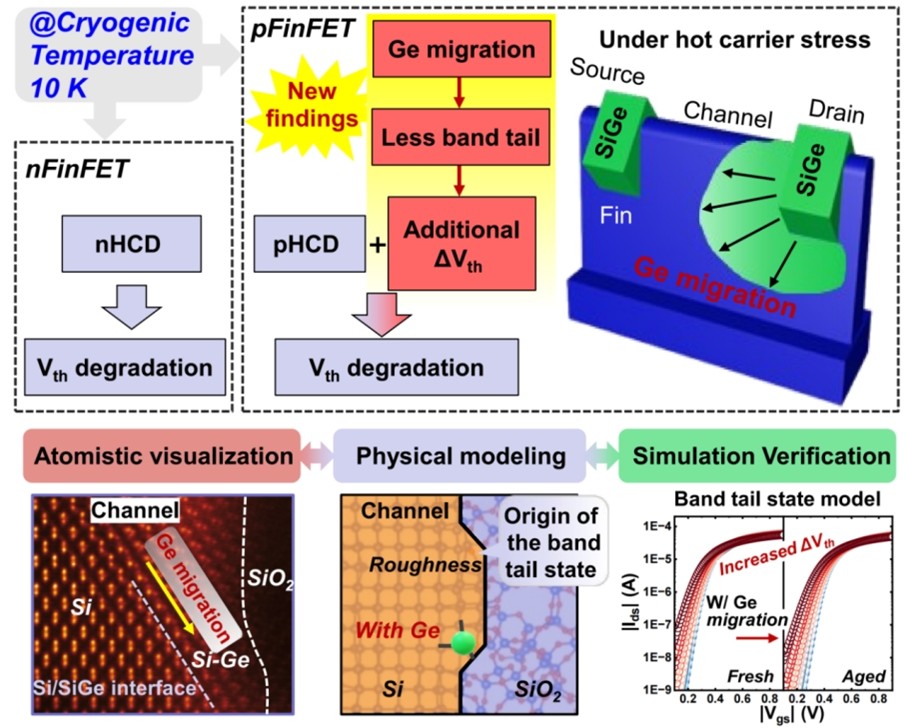

低温CMOS技术在高性能计算和量子计算中极具应用潜力,然而与常温相比,MOS器件在极低温下存在更严重的热载流子退化(HCD)的可靠性问题,成为制约其发展的关键瓶颈。同时低温HCD与带尾态等低温件物理效应紧密关联,导致其HCD呈现多物理机制耦合的特征,进一步加大了对低温可靠性研究的挑战。针对以上问题,吴幸教授团队与北京大学王润声教授团队以及中科院半导体研究所刘岳阳研究员团队合作,基于先进FinFET工艺,通过尖端的原位表征技术,系统解耦了极低温HCD的特性;首次在p型FinFET器件中观测到了极低温HCD过程中的显著额外阈值电压退化现象;通过原子级物理表征手段,发现了漏极Ge原子向沟道定向迁移的新机制;进一步结合第一性原理计算,阐明了Ge迁移通过抑制带尾态效应而引入额外阈值电压退化的物理机制;为厘清极低温HCD特性,优化低温CMOS制造工艺奠定了基础。该工作以“Towards Understanding Cryogenic Reliability in FinFETs under Hot Carrier Stress: New Findings on Ge Migration, and Impacts of Tail States Evolution”为题发表,文章第一作者是原位中心董作院和北京大学博士生王子瑞。通讯作者为吴幸教授、王润声教授以及刘岳阳研究员。

该工作的整体框架

二、针对高能效计算的新型双面垂直晶体管技术

当前2nm水平围栅器件即将大规模商用,但其也终将面临水平微缩的物理瓶颈。垂直围栅器件(VFET)受益于垂直方向的电流输运,可极大放宽水平微缩的尺寸限制,实现更高集成度;同时还可以进一步减小寄生电容,提升整体电路能效。在人工智能时代的高能效计算(EEC)大背景下,其是后摩尔时代的有利候选技术之一。但源漏不对称性、底部源漏引出造成的面积效率低等劣势也制约了VFET的进一步发展。北京大学吴恒研究员-黄如院士团队提出了一种全新的双面VFET(DSVFET)架构,巧妙的将底部源漏和引出置于晶圆背部,并结合双面电源和信号线的设计,可有效解决目前VFET的瓶颈问题。在此基础上,通过多项新工艺技术开发,在世界上首次验证了双面VFET的原型器件结构。还进一步开展了全面的DTCO评估,所提出的DSVFET架构在标准单元设计、芯片级别PPA等都显著优于FinFET,可节约39.8%的芯片面积,并实现15%的EDP收益,是未来高能效计算的有力竞争者。该工作以“ First Demonstration of Symmetric Dual-sided Vertical FET (DSVFET) for Energy Efficient Computing (EEC): From Processes and Devices to Circuits”为题发表,第一作者是北京大学博士生刘煜,通讯作者是吴恒研究员。原位中心吴幸教授、博士生李兰为合作者。

VLSI会议背景介绍

VLSI会议是超大规模集成电路和半导体器件领域最顶尖的国际会议之一,也是展示IC技术最新成果的重要窗口。该会议在国际集成电路和半导体器件的学术界以及工业界具有极高的学术地位和广泛影响力。会议论文不仅要具备学术创新,还要突显成果的产业价值和技术前沿性。每年,包括英特尔(Intel)、IBM、三星(Samsung)、IMEC和台积电(TSMC)等知名半导体公司都在该会议上发布他们最新的研究进展。2025年VLSI会议投稿难度大,Technology仅录用104篇。